spartan3Eスターターキット 149ドル 非常に安く(value)感じるのは気のせいか。 はたまたオプティマイズのEZ-FPGAか。 とりあえず、CQ誌のおまけデバイスで事足りるかもしれないので、x505とtp570にQuartusIIを淹れる。x505にパラレルポートはないのでtp570が書き込み専用。トラ技のおまけCPLD書き込めた。ないものはVerilogで作るしかないけど回路図入力のほうがやりやすいな。

500円で入手したグラフィックボードをガスコンロであぶって8bit140MSPS3chADCのAD9483KSなどをとる。 昔ノートPCで使ってたPC100のSDRAMをガスコンロであぶって1Mbit*16*4bankのSDRAMを4個とる。 16bitなので2個使えば3色分パラで読み書きできる。 60Hzだと16ms毎に同じアドレスに書くのでリフレッシュ不要。 しかし手配線は面倒な数。

ePanorama.net>VGA timing informationによると、VGAのHSは31469Hzで、ドットクロックはコレを800倍した25.175MHzらしい。

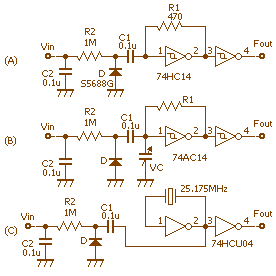

VCOのようなものをつくる。

バリキャップでなくとも、ダイオードは逆方向電圧を大きくすると空乏層幅が広くなってキャパシタンスが減る。

このキャパシタンスをCR発振のCに使えば、電位で発振周波数をコントロールできる(A)。

C1はDの逆方向電圧と発振電圧とをカップリングしてる。

C1とDを直列にしたときの合成容量は1/(1/C1+1/D)=D/(1+D/C1)なので、C1はDに対して十分大きければ無視できる。

R2はVinが低インピーダンスのときにC1が効いてしまうのを防ぐために入れてみた。

VCOのようなものをつくる。

バリキャップでなくとも、ダイオードは逆方向電圧を大きくすると空乏層幅が広くなってキャパシタンスが減る。

このキャパシタンスをCR発振のCに使えば、電位で発振周波数をコントロールできる(A)。

C1はDの逆方向電圧と発振電圧とをカップリングしてる。

C1とDを直列にしたときの合成容量は1/(1/C1+1/D)=D/(1+D/C1)なので、C1はDに対して十分大きければ無視できる。

R2はVinが低インピーダンスのときにC1が効いてしまうのを防ぐために入れてみた。

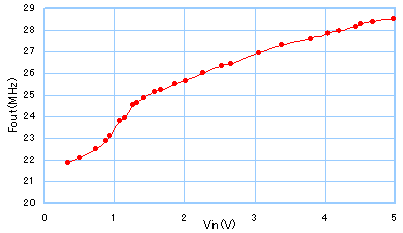

とりあえず、手持ちのパーツで(A)をブレッドボードに試作したら、グラフ(@13℃)のようになった。

これだと可変幅が広すぎてVinがシビアになってしまう。

(B)のようにして、あらかじめVCとR1で25.175MHz+αに設定しておけばVCより十分小さいDのキャパシタンスで微調整ということにできそう。

VCがDより大きいとなると、R1は小さくしなければならないから、74HC14では辛そう。

微調整がほんの数KHzでいいなら、25.175MHzの水晶(きっと千石の地下にある)を使ってしまって、Dのキャパシタンスで波形を歪ませて調節するくらいがちょうどいいかも(C)。

夜明け前より瑠璃色な:C:3倍速視聴。巧く描けばおもしろくなるんだろうけど残念。