2007年02月

2007/02/27 01:21:10

サークルカットできた。右が頒布物の内容を正確に表現できてるけど、左でポスト。鉛筆の下書きではもう少し左肩引けてたんだけど襟とか修正したら正面になってしまった。とりあえず、当たれ。

図書館で発振回路の設計と応用借りてきた。定数の決め方よくわかんね。2SK192Aなど買ってきてコルピッツVCOを実験してみたら、なにやら穴が開いている。なんだこれ?

携帯電話の電源を入れるとエラー画面で固まる。

リチウム電池の寿命らしいので延命を試みた。

電池パックを開けてコネクタを取り出し、リチウムイオン電池モジュールの代わりに単4電池*4を接続。

この状態でメールの送受信やEZwebはできるけど、通話はノイズが酷くてできない。

就活関連の電話を受けられないと困るので携帯電話を換える。W44K。

月面兎兵器ミーナ:K:録画中止。学園アリス:B:。

2007/02/20 08:10:39

8x16のドットマトリクスを16[本]のI/Oで使うアイデアは新奇性が高くて需要も期待できるから特許のようなものを出願してみようと思って検索すると既に取られてたorz。しかも最近。

[発明が解決しようとする課題]と[出願時期]をみるとP901iS(携帯電話)と関係がありそう。

詳細な説明を読んでみたけど、このアイデアでとても重要な、LEDの非線形特性から3つの状態を利用していることが書かれてないのはちょっと怪しい。公報の方法では諧調を電流制御でやってるから点灯したくないLEDも薄く点灯してしまう。その3状態を巧く使って時間軸ディザリングするべきなんだけどな。

学校で会社説明会。SEってのはどうなのかね?下流工程を知らないほうがスバラシイ仕様書を書けるというのは解るけど。Engineerでいいのか?プログラマを技能者クラスに持ってくればいいのか?

キャリアとは。スキルとは。技術とは。エンジニアとは。この辺りは分散が小さいから概念に関して世界のそれとシンクロできてきた。SEが求めているのはスキルで、プログラマやハード屋が求めているのは技術。哲学を楽しんでるわけではなくて。要求分析。

研究室の選択。研究室評価のために4年生の卒論発表を聞いたりしたけど、モデルの評価に最も論見通りなデータを示したり、ランダムサンプリングなのに1サンプルだったり、「みゅーめーとる」と言ったり、には失望。まぁ時間ないんだろうけど。自分も来年同じようなことするんだろうけど。ドクターは既に絶たれてるし、進学する価値のある学校なのか?進学or就職はまだ先に延ばす。

表示できた(゚∀゚)という例が他に見当たらないんだけど、どうなんでしょう つbmp2array.zip

エントリーシート記入のためキャラクターデザインをする。

キャラクターデザインは顔や髪型、服装などの見てくれを拘束することだとおもわれがちだけど、

キャラクターの内面や経験などのデザインが主となるべきもの。

はぴねす!:C:3倍速視聴

2007/02/13 03:44:35

C社説明会。あまり好い事ばかり言って不安要素を隠すと、

理系の学生には、この会社の経営陣は信用できない、という評価をされてしまうぞ。

しかも、説明会では質問するスキを与えない。

「面接の時に突っ込んでみて、答えをはぐらかしたり落とすようなら本当に不安な経営陣だ。」然しそんな余裕があるのか?

秋月でP-16購入。周波数カウンタが60MHzまで図れたり、P-10に比べてレンジが広くなってる。通販ページには書いてないけどマニュアルレンジと最大値最小値ホールド機能が付いてる。けど、表示の更新がかなり遅くなってて、レンジが十分ならP-10の方がいい感じ。

25.175MHzなんていう水晶は秋葉原では見つけられなかった。

そもそも、x505のVGAの出力のHSを周波数カウンタ(P-10)で測ってみると、640×480@60Hzで31.44kHzだったから、

ドットクロックは25.15MHzになって、水晶の可変範囲超えるし。

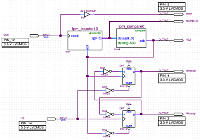

とりあえず(B)のVCOでpllを800倍に設定して動作確認。。。周波数が発散するorz。

いろいろ試すと37.91kHz(800×600@60Hz)の400倍は巧くいく。

周波数的にはP-10の測定限界(4dig)までロックしてそう、だけど、位相までロックできてるかは観測できない。

25MHzって蓑虫とブレッドボードで扱っていいものなのか(汗;。

とりあえず(B)のVCOでpllを800倍に設定して動作確認。。。周波数が発散するorz。

いろいろ試すと37.91kHz(800×600@60Hz)の400倍は巧くいく。

周波数的にはP-10の測定限界(4dig)までロックしてそう、だけど、位相までロックできてるかは観測できない。

25MHzって蓑虫とブレッドボードで扱っていいものなのか(汗;。

オシロとスペアナほすい。そうだ、140MSPSのADがあるからこれとDRAM、FPGAで高速データロガー作って、PCでオシロとスペアナ、、、って、趣味とはいえ遠回りしすぎ(笑)。

定本 発振回路の設計と応用。

勝手なモデル作って手探りするのは楽しいけど、これ読めば手軽にいろいろ解決できそう。

ガンダム0080:A:ポケットの中の戦争。

2007/02/06 06:16:33

spartan3Eスターターキット

149ドル

非常に安く(value)感じるのは気のせいか。

はたまたオプティマイズのEZ-FPGAか。

とりあえず、CQ誌のおまけデバイスで事足りるかもしれないので、x505とtp570にQuartusIIを淹れる。x505にパラレルポートはないのでtp570が書き込み専用。トラ技のおまけCPLD書き込めた。ないものはVerilogで作るしかないけど回路図入力のほうがやりやすいな。

500円で入手したグラフィックボードをガスコンロであぶって8bit140MSPS3chADCのAD9483KSなどをとる。

昔ノートPCで使ってたPC100のSDRAMをガスコンロであぶって1Mbit*16*4bankのSDRAMを4個とる。

16bitなので2個使えば3色分パラで読み書きできる。

60Hzだと16ms毎に同じアドレスに書くのでリフレッシュ不要。

しかし手配線は面倒な数。

ePanorama.net>VGA timing informationによると、VGAのHSは31469Hzで、ドットクロックはコレを800倍した25.175MHzらしい。

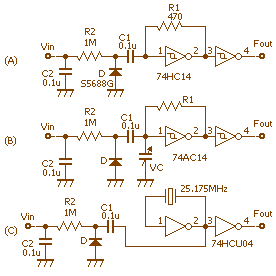

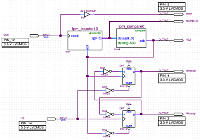

VCOのようなものをつくる。

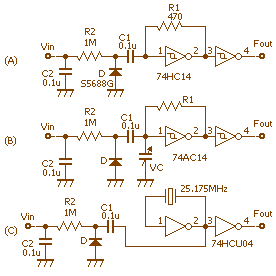

バリキャップでなくとも、ダイオードは逆方向電圧を大きくすると空乏層幅が広くなってキャパシタンスが減る。

このキャパシタンスをCR発振のCに使えば、電位で発振周波数をコントロールできる(A)。

C1はDの逆方向電圧と発振電圧とをカップリングしてる。

C1とDを直列にしたときの合成容量は1/(1/C1+1/D)=D/(1+D/C1)なので、C1はDに対して十分大きければ無視できる。

R2はVinが低インピーダンスのときにC1が効いてしまうのを防ぐために入れてみた。

VCOのようなものをつくる。

バリキャップでなくとも、ダイオードは逆方向電圧を大きくすると空乏層幅が広くなってキャパシタンスが減る。

このキャパシタンスをCR発振のCに使えば、電位で発振周波数をコントロールできる(A)。

C1はDの逆方向電圧と発振電圧とをカップリングしてる。

C1とDを直列にしたときの合成容量は1/(1/C1+1/D)=D/(1+D/C1)なので、C1はDに対して十分大きければ無視できる。

R2はVinが低インピーダンスのときにC1が効いてしまうのを防ぐために入れてみた。

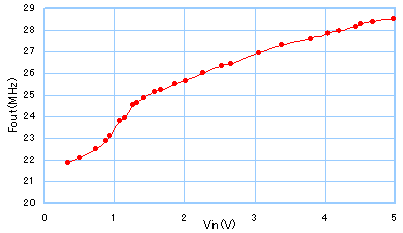

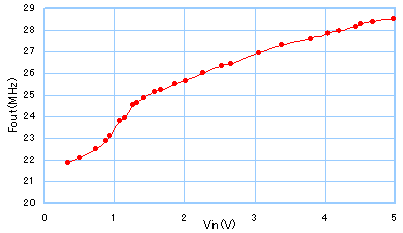

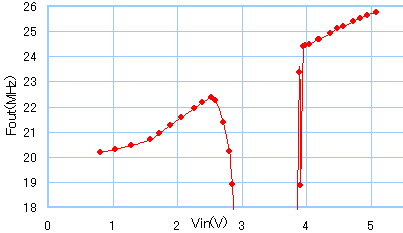

とりあえず、手持ちのパーツで(A)をブレッドボードに試作したら、グラフ(@13℃)のようになった。

これだと可変幅が広すぎてVinがシビアになってしまう。

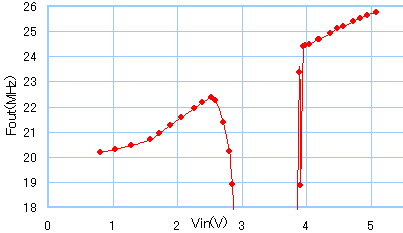

(B)のようにして、あらかじめVCとR1で25.175MHz+αに設定しておけばVCより十分小さいDのキャパシタンスで微調整ということにできそう。

VCがDより大きいとなると、R1は小さくしなければならないから、74HC14では辛そう。

微調整がほんの数KHzでいいなら、25.175MHzの水晶(きっと千石の地下にある)を使ってしまって、Dのキャパシタンスで波形を歪ませて調節するくらいがちょうどいいかも(C)。

夜明け前より瑠璃色な:C:3倍速視聴。巧く描けばおもしろくなるんだろうけど残念。

【最新】 かてごり 逆順

01 02 03 04 05 06 07 08 09 10 11 12 2003

01 02 03 04 05 06 07 08 09 10 11 12 2004

01 02 03 04 05 06 07 08 09 10 11 12 2005

01 02 03 04 05 06 07 08 09 10 11 12 2006

01 02 03 04 05 06 07 08 09 10 11 12 2007

01 02 03 04 05 06 07 08 09 10 11 12 2008

01 02 03 04 05 06 07 08 09 10 11 12 2009

01 02 03 04 05 06 07 08 09 10 11 12 2010

01 02 03 04 05 06 07 08 09 10 11 12 2011

01 02 03 04 05 06 07 08 09 10 11 12 2012

01 02 03 04 05 06 07 08 09 10 11 12 2013

01 02 03 04 05 06 07 08 09 10 11 12 2014

01 02 03 04 05 06 07 08 09 10 11 12 2015

01 02 03 04 05 06 07 08 09 10 11 12 2016

01 02 03 04 05 06 07 08 09 10 11 12 2017

01 02 03 04 05 06 07 08 09 10 11 12 2018

01 02 03 04 05 06 07 08 09 10 11 12 2019

01 02 03 04 05 06 07 08 09 10 11 12 2020

01 02 03 04 05 06 07 08 09 10 11 12 2021

01 02 03 04 05 06 07 08 09 10 11 12 2022

01 02 03 04 05 06 07 08 09 10 11 12 2023

01 02 03 04 05 06 07 08 09 10 11 12 2024

01 02 03 04 05 06 07 08 09 10 11 12 2025

01 02 03 04 2026

Copyright 2006 naru

naruken diary system

VCOのようなものをつくる。

バリキャップでなくとも、ダイオードは逆方向電圧を大きくすると空乏層幅が広くなってキャパシタンスが減る。

このキャパシタンスをCR発振のCに使えば、電位で発振周波数をコントロールできる(A)。

C1はDの逆方向電圧と発振電圧とをカップリングしてる。

C1とDを直列にしたときの合成容量は1/(1/C1+1/D)=D/(1+D/C1)なので、C1はDに対して十分大きければ無視できる。

R2はVinが低インピーダンスのときにC1が効いてしまうのを防ぐために入れてみた。

VCOのようなものをつくる。

バリキャップでなくとも、ダイオードは逆方向電圧を大きくすると空乏層幅が広くなってキャパシタンスが減る。

このキャパシタンスをCR発振のCに使えば、電位で発振周波数をコントロールできる(A)。

C1はDの逆方向電圧と発振電圧とをカップリングしてる。

C1とDを直列にしたときの合成容量は1/(1/C1+1/D)=D/(1+D/C1)なので、C1はDに対して十分大きければ無視できる。

R2はVinが低インピーダンスのときにC1が効いてしまうのを防ぐために入れてみた。